Testing and Design for Testability in VLSI

Last Updated :

28 Jun, 2025

In this article you will learn how testing ensures that VLSI chips work correctly and reliably after manufacturing. Testing is critical because faults can occur during fabrication, and catching them early prevents costly failures. We will cover the main types of faults, common testing methods, and how design-for-testability (DFT) techniques make testing faster and more effective. By the end, you’ll understand why testing is an essential part of the VLSI design cycle and how engineers design chips to be test-friendly.

VLSI Testing

Testing in VLSI is the process of verifying that a manufactured chip functions correctly and meets design specifications. Since manufacturing can introduce defects, testing helps identify faulty chips before they reach customers. Without testing, defective chips can cause system failures and increase costs. The main goals of testing are to detect manufacturing defects, ensure reliability, and maintain quality control. Testing also helps improve the design by identifying weak spots that need correction.

Effective testing saves time and money by catching faults early, making it a critical step in the VLSI production cycle.

Fault Models in VLSI

Fault models are simplified representations of defects that might occur in a chip. They help engineers predict and detect possible faults during testing.

Common fault models include:

- Stuck-at Faults: Signals stuck at logic 0 or 1, ignoring normal operation.

- Bridging Faults: Unwanted connections between two signal lines causing interference.

- Delay Faults: Signals arrive late, causing timing errors.

Using fault models, test patterns can be generated to efficiently detect these defects. Fault models simplify complex physical failures into manageable scenarios for testing.

VLSI Testing Techniques

There are several key testing methods used to verify VLSI chips:

- Functional Testing: Checks if the chip behaves as expected by applying input patterns and comparing outputs to expected results.

- Structural Testing: Focuses on the chip’s internal circuits and uses techniques like scan chains to test individual components and connections.

- Built-In Self-Test (BIST): Incorporates testing hardware within the chip to perform self-testing without external equipment.

- Automated Test Pattern Generation (ATPG): Software tools generate efficient test patterns based on fault models to maximize fault coverage.

These techniques ensure that chips are thoroughly tested for manufacturing defects before release.

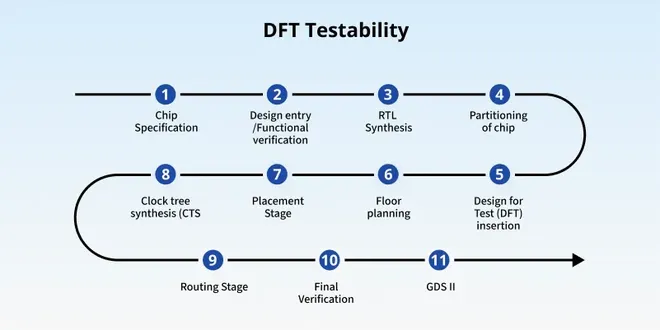

Design for Testability (DFT)

Design for Testability (DFT) involves adding features to a chip’s design that make testing easier and more effective. Without DFT, testing complex chips would be time-consuming and incomplete.

Common DFT methods include:

- Scan Design: Adds scan chains that allow internal flip-flops to be accessed and controlled during testing.

- Boundary Scan: Enables testing of interconnections between chips on a board without physical probes.

- Built-In Self-Test (BIST): Integrates test hardware into the chip to run tests internally.

DFT improves test coverage, reduces testing time, and lowers manufacturing costs by making faults easier to detect.

Test Compression and Test Cost Reduction

As chips grow more complex, the amount of test data and testing time increases significantly. Test compression techniques reduce the size of test data, speeding up testing and lowering costs. Compression methods minimize the number of test vectors needed without sacrificing fault coverage. This leads to faster tests and less memory required for test storage. Reducing test time and data size is critical for managing production costs and meeting tight manufacturing schedules.

Challenges in VLSI Testing

Testing modern VLSI chips faces several challenges:

- Increasing Complexity: More transistors and features make thorough testing harder and more time-consuming.

- Large Test Data Volume: Growing test data requires more storage and longer test times.

- Balancing Coverage and Overhead: Achieving high fault coverage without adding excessive design complexity or test cost is difficult.

- Detecting Subtle Faults: Some faults, like delay or transient faults, are harder to detect and require advanced testing techniques.

Addressing these challenges is essential to maintain chip quality and reliability in today’s advanced designs.

Explore

Electronic Devices & Components

Digital Circuits & Logic

Analog & Circuit Behavior

Solid-State Devices

Communication Systems

Signal Processing