IEEE 802.16e标准中LDPC编码的实现与仿真

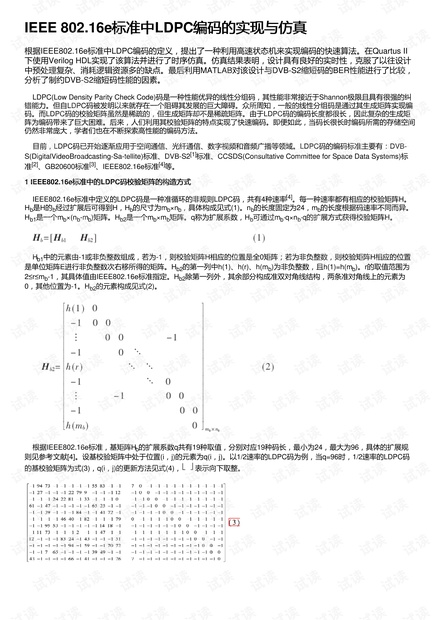

根据IEEE802.16e标准中LDPC编码的定义,提出了一种利用高速状态机来实现编码的快速算法。在Quartus II下使用Verilog HDL实现了该算法并进行了时序仿真。仿真结果表明,设计具有良好的实时性,克服了以往设计中预处理复杂、消耗逻辑资源多的缺点。最后利用MATLAB对该设计与DVB-S2缩短码的BER性能进行了比较,分析了制约DVB-S2缩短码性能的因素。 在现代无线通信和多媒体广播领域中,错误纠正编码技术的应用至关重要,而低密度奇偶校验(LDPC)编码因其优异的性能和纠错能力成为了研究的热点。特别是IEEE 802.16e标准中定义的LDPC码,其在实现过程中的复杂度和资源消耗问题也受到了广泛关注。为了解决这一挑战,本文提出了一种基于高速状态机的LDPC编码快速实现算法,并通过硬件描述语言Verilog HDL在FPGA平台上进行了编码的实现和仿真测试。 在深入探讨IEEE 802.16e标准定义的LDPC码之前,我们首先要了解LDPC码的基本概念。LDPC码是一种线性分组码,其特点是由稀疏矩阵定义,可以近似达到香农极限,从而提供极高的传输效率和错误纠正能力。LDPC码在编码过程中的计算复杂度相对较高,尤其是对于那些高码率的应用场景,这种复杂度往往会导致编码过程的延迟增加,同时消耗大量的逻辑资源。 IEEE 802.16e标准所规定的LDPC码具有四种不同的速率,并且每种速率都对应一种特定的校验矩阵H。这些校验矩阵由扩展后的Hb矩阵构成,其中Hb矩阵具有固定列数nb=24,而行数mb则随速率变化。这样的设计既满足了多速率传输的需求,又保持了编码过程的灵活性。 为了解决LDPC编码的复杂性问题,本文提出了一种使用高速状态机的编码算法。该算法通过优化线性方程组的操作来简化编码过程。具体来说,算法首先定义了一个状态机,该状态机能够高效地处理编码过程中的各种逻辑运算,并且通过合理配置状态转移来减少运算步骤,从而提高了编码速度和减少了所需资源。 在具体的实现环节,文章采用了Verilog HDL语言在FPGA上实现了LDPC编码电路。作者选择了q=24、速率1/2的LDPC码作为实验对象,并设计了相应的编码电路。在设计中,作者引入了kb个寄存器来存储输入序列与基矩阵乘积的更新值。通过循环移位计算输入数据,大幅减少了乘法运算的复杂度。这样的设计使得编码电路能够在保持较高效率的同时,最大程度地减少资源消耗。 通过在Quartus II软件环境下进行时序仿真,作者验证了设计的实时性和资源效率。与时域传统设计相比,该设计大幅度减少了预处理的复杂性和逻辑资源的消耗。同时,仿真结果还表明,该设计具备良好的实时性,能够满足现代通信系统对实时性的高要求。 为了进一步验证所提出算法的实际应用效果,作者利用MATLAB工具将LDPC编码设计与DVB-S2缩短码的误比特率(BER)性能进行了对比。通过分析两者的性能差异,揭示了限制DVB-S2缩短码性能的关键因素,并为后续的编码方案优化提供了重要的参考依据。 本文不仅详细介绍并实现了IEEE 802.16e标准中LDPC编码的快速算法,还在FPGA平台上进行了成功实现。通过深入分析和仿真测试,本文有效解决了LDPC编码在实际应用中编码复杂性和资源消耗的问题,并为无线通信系统的可靠性和效率提升提供了理论和技术支持。随着无线通信技术的不断发展和升级,LDPC编码技术有望在更多领域发挥其独特优势。

- 粉丝: 8

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- java毕业设计,航空销售管理系统

- java毕业设计,招生宣传管理系统

- 一个图书管理系统,java+swing

- java毕业设计,基于java敬老院管理系统

- java毕业设计,洗衣店订单管理系统

- 基于 Java 技术的医院病房舍管理系统设计与实现 基于 Java 平台的智能化病房舍病房综合管理系统开发 基于 Java 的智能化病房病房信息管理系统的设计 基于 Java 技术的智能化病房病房智能

- 网络文化对大学生思想品德的影响之社会实践.ppt

- 网络信息与国家安全.ppt

- 计算机的数据与编码.ppt

- 互联网+”大学生创新创业大赛项目计划书模版.doc

- 项目管理及六底盘损伤管理知识分析评估.pptx

- 日本政府投资项目管理体制研究.docx

- 网上在线购物系统项目管理.docx

- 通讯自动化培训—通讯自动化系统基础培训.pptx

- 网络营销你准备好了吗新生演讲.pptx

- 多目标优化实例和matlab程序.doc

信息提交成功

信息提交成功