Page Tables and Single-Level Paging

Last Updated :

03 Nov, 2025

A Page Table is a vital part of a computer’s memory management system. It acts like a guide for the CPU, translating the virtual addresses used by programs into actual physical addresses in RAM. This ensures that each process can access its own memory safely and efficiently, without interfering with other processes.

- The operating system (OS) maintains a page table for each process, and the Memory Management Unit (MMU) uses it to automatically handle address translation.

- The page number from a virtual address acts as an index into the table, and each row—called a Page Table Entry (PTE)—stores the mapping to physical memory.

Single Level Paging

Single Level PagingPage Table Structure

The page table’s structure defines how virtual addresses are mapped to physical memory and how memory usage is tracked for each process. Its components work together to make memory management both efficient and secure.

Stored in Main Memory

Page tables are usually stored in RAM, because they can become quite large, especially in systems with big virtual address spaces. Storing the table in main memory allows the OS to access and update it efficiently. While this adds a slight delay during address translation, it ensures smooth and effective memory management.

Managed by the Operating System (OS)

The OS is responsible for creating, maintaining, and updating page tables. Each process has its own table, which ensures memory isolation. This separation prevents one process from accidentally—or maliciously—accessing another process’s memory.

Located Using the Page Table Base Register (PTBR)

The Page Table Base Register (PTBR) is a special CPU register that stores the starting physical address of the current process’s page table. When the CPU switches between processes (a context switch), the PTBR is updated to point to the new process’s table. This lets the CPU quickly find the correct mapping for the process that is currently running.

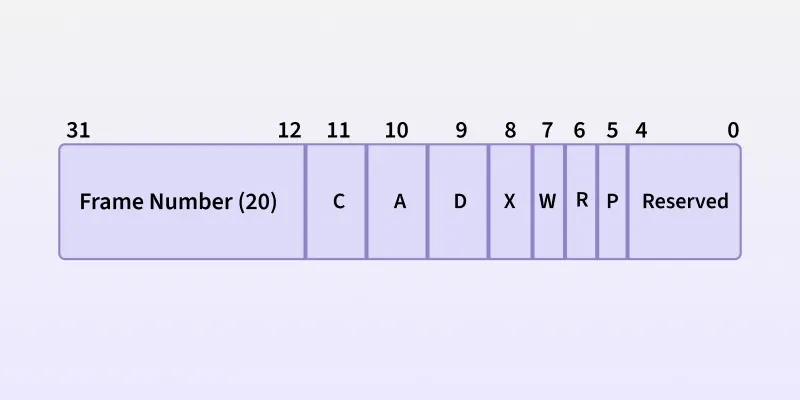

Page Table Entry (PTE): Fields and Their Roles

Each Page Table Entry (PTE) contains the metadata needed to manage and translate pages efficiently. While layouts can vary by architecture, a typical 32-bit PTE includes:

32-bit PTE

32-bit PTE1. Frame Number

Shows the physical frame in memory where the page resides. The number of bits needed is calculated as:

Frame bits = log2( Frame Size / Size of Physical Memory )

2. Present / Absent Bit (Valid / Invalid Bit) (P)

Tells whether the page is currently loaded in memory.

- 1 (Present): Page is in RAM

- 0 (Absent): Page is on disk, causing a page fault if accessed.

This supports demand paging, where pages are loaded only when needed.

3. Dirty Bit (Modified Bit) (D)

Set to 1 if the page has been modified since it was loaded. This ensures that only modified pages are written back to disk, saving unnecessary writes.

4. Reference / Accessed Bit (A)

Set automatically whenever the page is read or written. It helps page replacement algorithms like Least Recently Used (LRU) track which pages are actively used.

5. Protection Bits

Define access rights for the page:

- R: Read permission

- W: Write permission

- X: Execute permission

These bits protect memory from unauthorized or accidental access.

6. Caching Enabled / Disabled (C)

Determines whether the page can be cached. Useful for memory-mapped I/O, where fresh data from hardware is required instead of cached values.

Address Translation Using Single-Level Paging

In single-level paging, a virtual address is split into two parts:

| Field | Description |

|---|

| Page Number (p) | Indexes the page table to find the frame number. |

| Page Offset (d) | Specifies the exact location within the page/frame. |

Translation Process

- The MMU extracts the page number from the virtual address.

- It looks up the corresponding frame number in the page table.

- The frame number is combined with the page offset to generate the physical address.

This translation happens automatically, so programmers don’t need to handle it manually.

Example: Page Table Size Calculation

Let’s consider a 32-bit virtual address space with 4 KB pages.

Number of pages:

232 / 212=220

Its about 1 million pages per process.

If each Page Table Entry = 4 bytes, then

Page Table Memory:

220 × 4= 4 MB

This large memory requirement is a key limitation of single-level paging, leading to the development of multi-level paging structures in modern 64-bit systems.

Single-Level Paging Overhead

While single-level paging is conceptually simple, it introduces a few challenges:

- The entire page table must reside in memory, consuming large space for each process.

- Requires two memory accesses per data reference — one for the page table lookup, and another to access the actual data (partially solved using Translation Lookaside Buffers (TLBs)).

- Large contiguous space is needed for the page table, which becomes inefficient for sparse address spaces.

Despite these drawbacks, single-level paging provides a clear foundation for understanding more advanced paging structures.