Multilevel Paging in Operating System

Last Updated :

28 Dec, 2024

Multilevel paging is a memory management technique used in modern computer systems to efficiently handle large amounts of memory. It breaks down the virtual address space into smaller, more manageable pieces, organized into multiple levels of page tables.

Multilevel Paging consists of two or more levels of page tables in a hierarchical manner. It is also known as hierarchical paging. The entries of the level 1 page table are pointers to a level 2 page table and entries of the level 2 page tables are pointers to a level 3 page table and so on. The entries of the last level page table store actual frame information. Level 1 contains a single-page table and the address of that table is stored in PTBR (Page Table Base Register).

Multilevel paging in operating systems is a memory management technique which is used to manage large amounts of memory more efficiently. It breaks down the page table into smaller parts, which reduces the memory needed to store the page table. This approach is scalable, meaning it can handle larger memory sizes without becoming impractical.

Why Multi-Level Paging is Required?

Consider a 32-bit physical address space with page size = 4KB and let there be 220 = 1M, the total entries in the page table, page table entry size = 232 /212 = 220, and adding some protection bits and a dirty bit in the page table entry. Now page table size =220 * 24 = 3MB which should be in the physical memory and since each process has its own page table there is so much memory wastage only for storing page tables.

One solution to the large memory requirements of the page tables is to use multilevel paging, only the outermost page table will reside in the main memory and other page tables will be brought to the main memory as per the requirement because, at a particular time, we do not need complete page table, also we can save much memory space because outermost page table can fit in exactly one frame.

Levels in Paging

Levels in PagingIn multilevel paging whatever may be levels of paging, all the page tables will be stored in the main memory. So it requires more than one memory access to get the physical address of the page frame. One access for each level is needed. Each page table entry except the last level page table entry contains the base address of the next level page table.

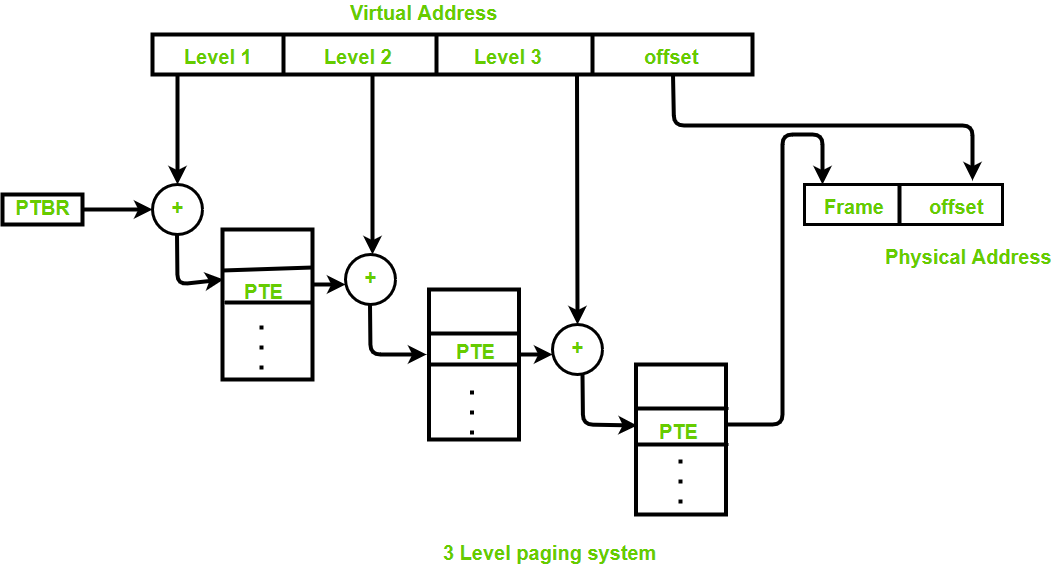

3-Level Paging System

3-Level Paging SystemReference to actual page frame:

- Reference to PTE in level 1 Page Table = PTBR Value + Level 1 Offset present in the Virtual Address.

- Reference to PTE in level 2 Page Table = Base address (present in Level 1 PTE) + Level 2 offset (present in VA).

- Reference to PTE in level 3 Page Table= Base address (present in Level 2 PTE) + Level 3 offset (present in VA).

- Actual page frame address = PTE (present in level 3).

Generally, the page table size will be equal to the size of the page.

Assumption: Byte addressable memory and n is the number of bits used to represent virtual address.

Important formula:

Number of entries in page table:

= (virtual address space size) / (page size)

= Number of pages

Virtual Address Space Size:

= 2n B

Size of Page Table:

<>= (number of entries in page table)*(size of PTE)

If page table size > desired size then create 1 more level.

Advantages of Multilevel Paging in Operating Systems

- Reduced memory overhead: Multilevel paging can help to reduce the memory overhead associated with the page table. This is because each level contains fewer entries, which means that less memory is required to store the page table.

- Faster page table lookup: With a smaller number of entries per level, it takes less time to perform a page table lookup. This can lead to faster system performance overall.

- Flexibility: Multilevel paging provides greater flexibility in terms of how the memory space is organized. This can be especially useful in systems with varying memory requirements, as it allows the page table to be adjusted to accommodate changing needs.

Disadvantages of Multilevel Paging in Operating Systems

- Increased complexity: Multilevel paging adds complexity to the memory management system, which can make it more difficult to design, implement, and debug.

- Increased overhead: Although multilevel paging can reduce the memory overhead associated with the page table, it can also increase the overhead associated with page table lookups. This is because each level must be traversed to find the desired page table entry.

- Fragmentation: Multilevel paging can lead to fragmentation of the memory space, which can reduce overall system performance. This is because the page table entries may not be contiguous, which can result in additional overhead when accessing memory.

Problem For Practice

Q. Consider a virtual memory system with physical memory of 8GB, a page size of 8KB, and a 46-bit virtual address. Assume every page table exactly fits into a single page. If page table entry size is 4B then how many levels of page tables would be required?

Explanation:

Page size = 8KB = 213 B

Virtual address space size = 246 B

PTE = 4B = 22 B

Number of pages or number of entries in page table,

= (virtual address space size) / (page size)

= 246B/213 B

= 233

Size of Page Table,

= (number of entries in page table)*(size of PTE)

= 233*22 B

= 235 B

To create one more level,

Size of Page Table > Page Size

Number of page tables in last level,

= 235 B / 213 B

= 222

The base address of these tables is stored in the page table [second last level].

Multi-Level Paging

Multi-Level PagingSize of page table [second last level]

= 222*22B

= 224B

To create one more level,

Size of page table [second last level] > page size

Number of page tables in second last level

= 224B/213 B

= 211

The base address of these tables are stored in page table [third last level]

Size of page table [third last level]

= 211*22 B

= 213 B

= page size

∴ 3 levels are required.

Similar Reads

Paging in Operating System Paging is the process of moving parts of a program, called pages, from secondary storage (like a hard drive) into the main memory (RAM). The main idea behind paging is to break a program into smaller fixed-size blocks called pages.To keep track of where each page is stored in memory, the operating s

8 min read

Prepaging in Operating System Prerequisite – Virtual Memory in Operating System As suggested by the concept of virtual memory, it is not necessary that the entire process should be loaded into the main memory at the given time. The process can be executed efficiently if only some of the pages are present in the main memory at a

4 min read

Multi Processing Operating System The operating system functions like a manager of all the available resources. Therefore operating system is defined as an interface between the system and the user. There are various types of operating systems such as Batch Operating Systems, Multi-programming Operating Systems, distributed operatin

4 min read

Lazy Swapping in Operating System Pre-requisites: Swapping in Operating System Lazy swapping, also known as demand paging, is a memory management technique used in operating systems to allow programs to access more memory than is physically available in the system. Increasing the degree of multi-programming of the system means incre

2 min read

Spooling in Operating System In the Operating System, we had to provide input to the CPU, which then executed the instructions and returned the output. However, there was a flaw in this strategy. In a typical situation, we must deal with numerous processes, and we know that the time spent on I/O operations is very large in comp

4 min read

Multiprogramming in Operating System As the name suggests, Multiprogramming means more than one program can be active at the same time. Before the operating system concept, only one program was to be loaded at a time and run. These systems were not efficient as the CPU was not used efficiently. For example, in a single-tasking system,

5 min read

What is Demand Paging in Operating System? Demand paging is a memory management scheme used in operating systems to improve memory usage and system performance. Let's understand demand paging with real life example Imagine you are reading a very thick book, but you don’t want to carry the entire book around because it’s too heavy. Instead, y

10 min read

Inverted Page Table in Operating System Most Operating Systems implement a separate page table for each process, i.e. for the 'n' number of processes running on a Multiprocessing/ Timesharing Operating System, there is an 'n' number of page tables stored in the memory. Sometimes when a process is very large and it occupies virtual memory

7 min read

Multi-User Operating System An operating system is software that acts as an interface between the user and the computer hardware which does multiple functions such as memory management; file management and processor management. The operating system should have to meet the requirements of all its users in a balanced way so that

5 min read

Memory Protection in Operating Systems In this article, we will be discussing memory protection in operating systems. As we know that different operating systems use different forms of memory protection or separation which consists of Plan9 and Inferno, Microsoft Windows, etc. In Memory protection, we have to protect the operating system

5 min read