Smart traffic light controller using verilog

- 1. 1 DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING PONDICHERRY UNIVERSITY SMART TRAFFIC LIGHT CONTROLLER USING VERILOG GUIDED BY PROF. Dr. P. SAMUNDISWARI Dept. Of Electronics Engineering PRESENTED BY BEULAH .A VAISHALI .K M.Tech (ECE)-Ist yr

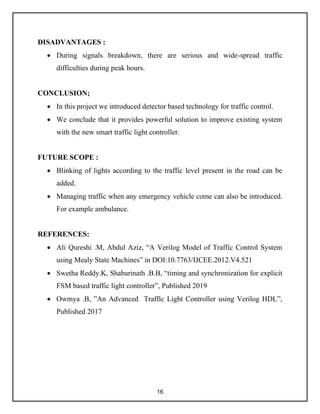

- 2. 2 CONTENTS S. NO. TOPIC PAGE NO. 1 OBJECTIVE 3 2 INTRODUCTION 3 3 BLOCK DIAGRAM 4 4 WORKING PRINCIPLE 5 5 STATE DIAGRAM 6 6 CODE 7 7 TEST BENCH 10 8 SIMULATION OUTPUT 11-15 9 ADVANTAGES AND DISADVANTAGES 15 -16 10 CONCLUSION 16 11 REFERENCES 16

- 3. 3 OBJECTIVE: • The main aim of the project is to design a two way traffic light controller using verilog. • One with the help of timing mechanism and other by the help of detector or sensor. SOFTWARE USED: • Xilinx 14.7 • Verilog: C like HDL is easier to comprehend and saves design time since the syntax is more concise that VHDL INTRODUCTION: • In general, many traffic lights are operates on a timing mechanism that changes the light after given time interval. • The traffic light system consists of three important parts, in that traffic light controller is first one, because of it represent brain of the traffic system. • The second part is the signal visualization or in simple words is signal face. • The third part is the detector or sensor. TRAFFIC LIGHTS: • An intelligent traffic light system senses the presence or absence of vehicles and reacts accordingly. • The idea behind intelligent traffic systems is that drivers will not spend unnecessary time waiting for the traffic lights to change. • In the traffic light control system, the main controller, control circuit, counter, timer, decoder, clock signal generator, decoder drive circuit and digital display decoder drive circuit are needed to complete the whole process of controlling the traffic light.

- 4. 4 BLOCK DIAGRAM: EXPANDED RTL VIEW:

- 5. 5 WORKING PRINCIPLE; • The main road's lights are always green for the major traffic to pass. • The main road's lights turn red only when there is a car on either side of the side road for a period of time. • When detector detect the vehicles, only then the lights on the side road turn from red->green while the main road's lights turn from green->yellow->red. • After the given interval of time, lights on the main road turns to red- >yellow->green and the side road turns from green->red. • In the timer part, there are three things one is the short time pulse (TS) and

- 6. 6 the long time pulse (TL) and the last is a response to start the timer (ST) signal. STATE DIAGRAM: • The main road will be green until no cars are found and it remains in state S0. • When long time expires and cars found the transition from S0 to S1 takes place. • When the short time interval expires it transit from S1 to S2. • When the long time interval doesn't expire and cars are detected it will in the state S2. • When the long time expires and no more cars detected it transit from S2 to S3. • When the short interval expires it transit from S3 to S0 and the cycle continues.

- 7. 7 CODE: MAIN MODULE: `timescale 1ns / 1ps module main( output MR, output MY, output MG, output SR, output SY, output SG, input reset, input C, input Clk ); timer part1(TS, TL, ST, Clk); fsm part2(MR, MY, MG, SR, SY, SG, ST, TS, TL, C, reset, Clk); endmodule TIMER MODULE: `timescale 1ns / 1ps module timer( output TS, output TL, input ST, input Clk ); integer value;

- 8. 8 assign TS=(value>=4); assign TL=(value>=14); always@(posedge ST or posedge Clk) begin if(ST==1)begin value=0; end else begin value=value+1; end end endmodule FSM MODULE: `timescale 1ns / 1ps module fsm( output MR, output MY, output MG, output SR, output SY, output SG, output ST, input TS, input TL, input C, input reset,

- 9. 9 input Clk ); reg [6:1] state; reg ST; parameter mainroadgreen= 6'b001100; parameter mainroadyellow= 6'b010100; parameter sideroadgreen= 6'b100001; parameter sideroadyellow= 6'b100010; assign MR = state[6]; assign MY = state[5]; assign MG = state[4]; assign SR = state[3]; assign SY = state[2]; assign SG = state[1]; initial begin state = mainroadgreen; ST = 0; end always @(posedge Clk) begin if (reset) begin state = mainroadgreen; ST = 1; end else begin ST = 0; case (state) mainroadgreen: if (TL & C) begin state = mainroadyellow; ST = 1; end mainroadyellow:

- 10. 10 if (TS) begin state = sideroadgreen; ST = 1; end sideroadgreen: if (TL | !C) begin state = sideroadyellow; ST = 1; end sideroadyellow: if (TS) begin state = mainroadgreen; ST = 1; end endcase end end endmodule TEST BENCH: `timescale 1ns / 1ps module fsm_test; // Inputs reg TS; reg TL; reg C;reg reset; reg Clk; // Outputs wire MR; wire MY; wire MG; wire SR; wire SY; wire SG; wire ST; // Instantiate the Unit Under Test (UUT) fsm uut ( .MR(MR), .MY(MY), .MG(MG), .SR(SR), .SY(SY), .SG(SG), .ST(ST), .TS(TS), .TL(TL), .C(C), .reset(reset), .Clk(Clk) ); initial begin // Initialize Inputs TS = 0;TL = 0;C = 0;reset = 1;

- 11. 11 Clk = 0; #100; TS=0;TL=1;C=1;reset=0; #100; TS=0;TL=0;C=0;reset=1; #100; TS=1;TL=1;C=0;reset=0; #100; end always begin #100 Clk=~Clk; end endmodule SIMULATION OUTPUT:

- 12. 12

- 15. 15 ADVANTAGES: • Traffic signals help for movement of traffic securely without any collision. • The drivers will not spend unnecessary time waiting for the traffic lights to change. • Traffic control by signals is accurate and economical as compared to traffic police control.

- 16. 16 DISADVANTAGES : • During signals breakdown, there are serious and wide-spread traffic difficulties during peak hours. CONCLUSION; • In this project we introduced detector based technology for traffic control. • We conclude that it provides powerful solution to improve existing system with the new smart traffic light controller. FUTURE SCOPE : • Blinking of lights according to the traffic level present in the road can be added. • Managing traffic when any emergency vehicle come can also be introduced. For example ambulance. REFERENCES: • Ali Qureshi .M, Abdul Aziz, “A Verilog Model of Traffic Control System using Mealy State Machines” in DOI:10.7763/IJCEE.2012.V4.521 • Swetha Reddy.K, Shabarinath .B.B, “timing and synchronization for explicit FSM based traffic light controller”, Published 2019 • Owmya .B, ”An Advanced Traffic Light Controller using Verilog HDL”, Published 2017

![9

input Clk

);

reg [6:1] state;

reg ST;

parameter mainroadgreen= 6'b001100;

parameter mainroadyellow= 6'b010100;

parameter sideroadgreen= 6'b100001;

parameter sideroadyellow= 6'b100010;

assign MR = state[6];

assign MY = state[5];

assign MG = state[4];

assign SR = state[3];

assign SY = state[2];

assign SG = state[1];

initial begin state = mainroadgreen; ST = 0; end

always @(posedge Clk)

begin

if (reset)

begin state = mainroadgreen; ST = 1; end

else

begin

ST = 0;

case (state)

mainroadgreen:

if (TL & C) begin state = mainroadyellow; ST = 1; end

mainroadyellow:](https://image.slidesharecdn.com/smarttrafficlightcontrollerbybeulahandvaishaliesandvlsiassignment-220223161733/85/Smart-traffic-light-controller-using-verilog-9-320.jpg)